# Transcendental and Optimized Digital Designing using Reversible Logic

# Divyansh Mathur, Prachi Singh, Sunita Singh

Abstract – In [1] we have presented a novel design of different Digital Arithmetic and Logic Units using basic Reversible Gates. The current issue presents and emphasises on the use of Ultimate Optimized Design of digital circuits such as Adders, Subtracters, and 1-Bit Comparator. Furthermore, the Optimized Design does not give any ambiguous values in the terms of Quantum Cost associated with the circuit.

Index Terms -Ancillary Inputs, Quantum Cost, TR Gate.

# I. INTRODUCTION

The approach in the Reversible Logic Design differs significantly from the traditional Combinational Logic Design. In Reversible Logic Circuit, the number of input lines should be equal to the number of output lines with each output line being used only once thereby making the resulting circuit acyclic<sup>[10]</sup>. Thus a Reversible Logic Gate is an n-input, n-output device with one-to-one mapping. This helps in the determination of the outputs from the inputs and vice-versa, i.e. there is one-to-one correspondence between the input and the output vectors. The main challenges are reducing the hardware complexity, delay, quantum cost, power dissipation, garbage outputs and the overall number of constant ancillary inputs used in the Logical Unit's Design.

Energy loss in Digital Designing is an important factor for marking the level of performance. While some portion of the energy is dissipated due to non-ideality of switches, the other results from the quality of materials used. Though heat loss has been dramatically reduced by complex integration levels and high-end fabrication processes, the part of reducing energy dissipation in Digital Circuits is still left undone. It is here that the Reversible Logic shows its effect and its applications in promising computer paradigms with applications, Quantum Dot Cellular Automata, Optical Computing etc.<sup>[4, 5, 6, 7, 8, 9]</sup>. Bennet<sup>[11]</sup> had observed that if a computation is carried out on Reversible Logic, zero energy dissipation is possible, as the amount of energy dissipated in a system is directly in relation to the number of bits erased during that computation.

#### Manuscript received on February, 2013

**Divyansh Mathur,** Department of Electronics and Communication, Pranveer Singh Institute of Technology – College of Engineering, Kanpur, India.

**Prachi Singh,** Department of Electronics and Communication, Pranveer Singh Institute of Technology – College of Engineering, Kanpur, India.

**Dr. Sunita Singh**, Department of Applied Sciences, Pranveer Singh Institute of Technology, Kanpur, India.

Since Normal Combinational Logic Circuits dissipate heat for every bit of information lost during their operation, the recovery of a piece of information once lost is completely impossible. However, if the same circuit is constructed using the Reversible Logic Gates, chances are high not only of therecovery of that piece of information but also reducing the heat losses. Demonstrated by R. Landauer in 1960s, the energy dissipation for every bit of information exchange, associated with even high-tech systems designed with traditional and irreversible logic was numerically equal to kT.ln2; wherein k is described as the Boltzmann Constant and T as the absolute temperature at which the operation is being performed<sup>[1]</sup>.

As stated previously, designing of digital circuits using the Reversible Logicis an on a grow technique which is steadfastly paving its way into Digital Electronics, Quantum Cost is one of the major factors playing a pivotal role in the designing of Arithmetic and Logical Units.

Quantum Cost, the cost of a circuit, refers to the overall expenses, pertaining to the use of Reversible Logic Gates for synthesising a given Logical Function, incurred in designing of the circuit in terms of the cost of the primitive Reversible Logic Gates used. The Quantum Cost of the circuit is determined by calculating the *already known* cost of the primitive gates required for realizing the Arithmetic and Logic Circuit Units.

Other factors effecting the realization of different Digital Arithmetic and Logic Circuits are *Ancillary Inputs,Garbage Outputs*, and *Delay. Ancillary Inputs* are the inputs which have a constant value of either 0 or 1, provided at the input terminals of the Reversible Logic Gates, and have to be maintained at a constant value in order to synthesise the given Logical Function, as per the requirements.On the other hand *Garbage Outputs* are those output vectors that are left unutilised. Though the *Garbage Outputs* on to perform any useful operation, yet they are present in order to maintain the reversibility of the circuit<sup>[1]</sup>.

As the Moore's Law holds and will alwayscontinue to hold, the number of chip components keep getting doubled in every one and a half years;the designing of digital circuits using the traditional combinational logic would not only cause a high rate of dissipation of energy in form of heat and information loss in the circuits, but also reduce the circuit's performance and life to a great extent. Designingin this way would not fulfil the desired purpose of achieving the efficiency, the demand in today's silicon world.

This paperis thereforepresented here to meet the much required standards for the need of efficientandoptimizeddesign models of digital circuits such as Adders, Subtracters, and 1-Bit Comparatorusing onlybasic Reversible Logic Gates who's Quantum Cost is known, established, and unambiguous.

# **II. BASIC REVERSIBLE GATES**

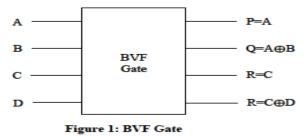

#### **BVF** Gate **A**.

With Quantum Cost of two, the BVF Gate is a 4x4 Reversible Gate described as follows:

$I_V = (A, B, C, D)$

$O_V = (P=A, Q=A \oplus B, R=C, S=C \oplus D)$

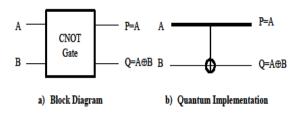

Feynman/CNOT Gate[15] **B**.

It's a 2x2 Reversible Gate having a Quantum Cost of one and described as under:

$I_V = (A, B)$

$O_V = (P = A, Q = A \oplus B)$

Figure 2: Feynman/CNOT Gate

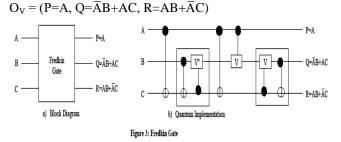

#### С. Fredkin Gate[13]

The Fredkin is an advanced 3x3 Reversible Gate with a Quantum Cost of five and description given by:

$I_V = (A, B, C)$

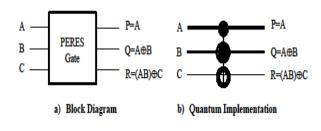

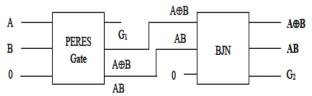

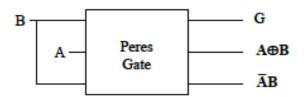

#### D. Peres Gate[14]

It's a 3x3 Reversible Gate, constructed from one CNOT and one Toffoli Gate having a Quantum Cost of four and described by:

$I_V = (A, B, C)$

$$O_V = (P=A, Q=A \oplus B, R=(AB) \oplus C)$$

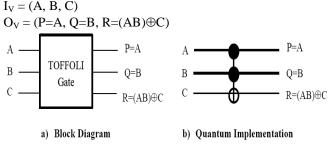

#### Е. Toffoli Gate[12]

It has a Quantum Cost of five and described by:

# III. DESIGN MODELS USING REVERSIBLE GATES

### A. Design Model of Half Adder

A Half Adder is a Logical CircuitUnit designed to add two binary bits and provide the output in terms of Sum and Carry.

$SUM = A \oplus B$

CARRY = AB

The truth table is illustrated as: Table 1. Half Adder Truth Table

| Table 1. Hall Adder Fruth Table |      |       |      |

|---------------------------------|------|-------|------|

| IN                              | PUTS | OUT   | PUTS |

| A                               | В    | CARRY | SUM  |

| 0                               | 0    | 0     | 0    |

| 0                               | 1    | 0     | 1    |

| 1                               | 0    | 0     | 1    |

| 1                               | 1    | 1     | 0    |

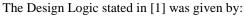

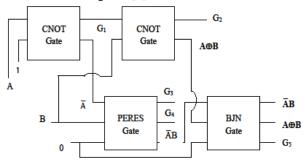

### Figure 6: Half Adder using Peres and BJN Gate

The optimized design of the circuit is now shown:

# **Figure 7: Optimized Half Adder**

With this optimized design approach we can hereby

conclude that this design is in itself and additional no

43

complete

requires

Published By: Blue Eyes Intelligence Engineering & Sciences Publication

modifications when Quantum Cost and other parameters are concerned. The following table establishes the facts stated above:

| PARAMETERS                       | Figure 6 | Figure 7 |

|----------------------------------|----------|----------|

| Garbage Outputs                  | 2        | 1        |

| Logic Gates Used                 | 2        | 1        |

| Constant Ancillary Inputs Number | 2        | 1        |

| Quantum Cost                     | 9        | 4        |

| Improvement in Quantum Cost      | +55.56%  |          |

# Table 2: Comparison of Different Designs of Half Adder

# B. Design Model of Half Subtracter

Made for the purpose of carrying out the task of finding the difference between twobinary bits, the Logical Unit of the Half Subtracter is discussed here. The two output terms are as follows:

> DIFFERENCE =  $A \oplus B$  $BORROW = \overline{A}B$ Table 3: Half Subtracter Truth Table

| Table 5, Hall Subtracter Fruth Fable |     |        |            |

|--------------------------------------|-----|--------|------------|

| INP                                  | UTS | OUT    | PUTS       |

| A                                    | B   | BORROW | DIFFERENCE |

| 0                                    | 0   | 0      | 0          |

| 0                                    | 1   | 1      | 1          |

| 1                                    | 0   | 0      | 1          |

| 1                                    | 1   | 0      | 0          |

The conventional logic in [1] was:

Now the optimized design for the same is:

Figure 9: Optimized Half Subtracter

From the above two figures we can conclude that the optimized design is not only simple in construction but also efficient in terms of the Quantum Cost.

| Table 4: Compa | arison of Different Designs ( | of Half Subtracter |

|----------------|-------------------------------|--------------------|

| METEDS         | Eigung 0                      | Figure 0           |

| PARAMETERS                       | Figure 8 | Figure 9 |  |

|----------------------------------|----------|----------|--|

| Garbage Outputs                  | 5        | 1        |  |

| Logic Gates Used                 | 4        | 1        |  |

| Constant Ancillary Inputs Number | 2        | 0        |  |

| Quantum Cost                     | 11 4     |          |  |

| Improvement in Quantum Cost      | +63.64%  |          |  |

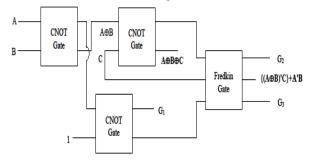

# C. Design Model of Full Adder

An advancement of the Half Adder, the Full Adder is a circuit designed to perform the summation operation onthree binary bits.

The method cum operation of the Logical Unit is same as that of the Half Adder but with an additional binary bit. The outputs of the Full Adder are also represented as SUM and CARRY, and these are described by the following values:

### $SUM = A \oplus B \oplus C$

$CARRY = \{(A \oplus B)C\} + (AB)$

The value of variable CARRY can also be given by  $\{(A \oplus B)C\} \oplus (AB), as they yield same results.$

Thetruth table of the Full Adder is given in the table below: Table 5: Truth Table of Full Adder

| INPUTS |   |   | OUTPUTS |     |  |

|--------|---|---|---------|-----|--|

| A      | В | С | CARRY   | SUM |  |

| 0      | 0 | 0 | 0       | 0   |  |

| 0      | 0 | 1 | 0       | 1   |  |

| 0      | 1 | 0 | 0       | 1   |  |

| 0      | 1 | 1 | 1       | 0   |  |

| 1      | 0 | 0 | 0       | 1   |  |

| 1      | 0 | 1 | 1       | 0   |  |

| 1      | 1 | 0 | 1       | 0   |  |

| 1      | 1 | 1 | 1       | 1   |  |

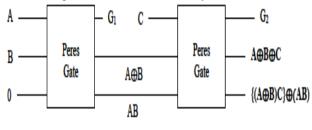

Keeping in mind the values of the outputs, the Half Adder has been described and realizedusing two cascaded Peres Gates with a minimum Quantum Cost of 8. It has been shown in [17] and [19] that any Reversible Logic realisation of Full Adder Circuit includes at least two garbage outputs and one constant input. The authors in [16-19] have given a Quantum Cost efficient Reversible Full Adder Circuit that is realised using two 3x3 Peres Gates only.

# Figure 10: Full Adder Using Peres Gate

The optimized design for the same follows as:

Published By:

& Sciences Publication

# Figure 11: Optimized Full Adder

In this circuit not only has the Quantum Cost been reduced but the Constant Ancillary Input removed, implying that the above stated design and its corresponding references can follow this new improved model. Here the energy dissipation is considerably lowered as there is no constant ancillary input which may consume power from any external source.

Further we would like to add that we don't disagree on the proposed designs but simply present our new optimized model which can be used to improve circuit performance and life.

The Comparison Table illustrates the things that were stated above:

| PARAMETERS                       | Figure 10 | Figure 11 |

|----------------------------------|-----------|-----------|

| Garbage Outputs                  | 2         | 2         |

| Logic Gates Used                 | 2         | 2         |

| Constant Ancillary Inputs Number | 1         | 0         |

| Quantum Cost                     | 8         | 7         |

| Improvement in Quantum Cost      | +12.5%    |           |

Table 6: Comparison of Different Designs of Full Adder

#### D. Design Model of Full Subtracter

With similar working as that of its counterpart, the Full Subtracter is used to subtract three and not just two binary bits. The output values are:

> DIFFERENCE =  $A \oplus B \oplus C$ BORROW = { $(A \oplus B)'C$ } $\oplus (\overline{A}B)$

Truth Table is shown below: Table 7. Touch Table of Table On the

|   | INPUTS |   | OUT    | TPUTS      |

|---|--------|---|--------|------------|

| A | B      | С | BORROW | DIFFERENCE |

| 0 | 0      | 0 | 0      | 0          |

| 0 | 0      | 1 | 1      | 1          |

| 0 | 1      | 0 | 1      | 1          |

| 0 | 1      | 1 | 1      | 0          |

| 1 | 0      | 0 | 0      | 1          |

| 1 | 0      | 1 | 0      | 0          |

| 1 | 1      | 0 | 0      | 0          |

| 1 | 1      | 1 | 1      | 1          |

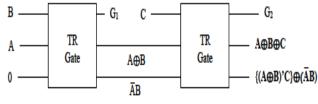

The design shown below is taken from [2] & [3].

# Figure 12: Full Subtracter Using TR Gate

The designing of Subtracters has always been an issue in terms of Quantum Cost. Instead of using a proposed gate exclusively for subtracters<sup>[2]</sup>, we are citing an optimized

model which doesn't give any ambiguous values in terms of Quantum Cost, and uses basic Reversible Gates in place of the proposed TR Gate. Although the optimized model isn't efficient in terms of number of gates used & the number of garbage outputs, but still we have tried our level best in maintaining the Quantum Cost of the circuit taking into account the upperas well as the lower bound limit of the proposed TR Gate's Quantum Cost. If the upper bound is taken as  $6^{[2]}$  then overall cost jumps to 12 while the lower bound of  $4^{[3]}$  drops its value to 8.

With this in mind, the optimized circuit undoubtedly matches the minimum value of Quantum Cost.

Figure 13: Optimized Full Subtracter

The analytical study is shown in the table below:

Table 8: Comparison of Different Designs of 1-Bit Comparator

| Table 6. Comparison of Different Designs of 1-Dir Comparator |                                |  |           |

|--------------------------------------------------------------|--------------------------------|--|-----------|

| PARAMETERS                                                   | Figure 12                      |  | Figure 13 |

| Garbage Outputs                                              | 2                              |  | 3         |

| Logic Gates Used                                             | 2                              |  | 4         |

| Constant Ancillary Inputs Number                             | 1                              |  | 1         |

| Quantum Cost                                                 | 12 (if taken 6) 8 (if taken 4) |  | 8         |

| Improvement in Quantum Cost                                  | +33.33% (for 12) & ±0% (for 8) |  |           |

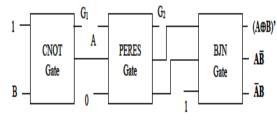

### E. Design Model of 1-Bit Comparator

A 1-Bit Comparator is a Logical Circuit designed to compare two binary numbers, each having one bit. The output is taken in three states,  $F_{A\!<\!B}$  ,  $F_{A\!=\!B}$  and  $F_{A\!>\!B},$ respectively.

By the name it has, the 1-Bit Comparator logic circuit works by comparing each of the bits of the two binary input numbers. When one bit is at logic low and the other at logic high, comparison is done by checking which bit belongs to which number and the output can either be  $F_{A < B}$  or  $F_{A > B}$ . On the other hand, when both the bits are at logic low or logic high, then the output is certainly  $F_{A=B}$ .

The corresponding truth table is shown:

Table 9: 1-Bit Comparator Truth Table

| INP | UTS |                  | OUTPUTS          |                     |

|-----|-----|------------------|------------------|---------------------|

| A   | B   | F <sub>A⊲B</sub> | F <sub>A=B</sub> | F <sub>A&gt;B</sub> |

| 0   | 0   | 0                | 1                | 0                   |

| 0   | 1   | 1                | 0                | 0                   |

| 1   | 0   | 0                | 0                | 1                   |

| 1   | 1   | 0                | 1                | 0                   |

Based on the above truth table the output assumes form in three different cases elaborated as:

$F_{A < B} = \overline{A}B$  $F_{A=B} = \overline{A}\overline{B}+AB =$ (A⊕B)'

Published By:

$$F_{A>B} = A\overline{B}$$

& Sciences Publication

Retrieval Number: D0187021413/2013©BEIESP

# International Journal of Emerging Science and Engineering (IJESE) ISSN: 2319-6378, Volume-1 Issue-4, February 2013

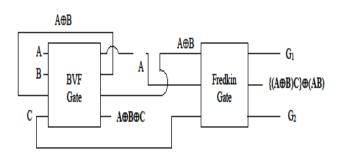

The design published in [1] is as follows:

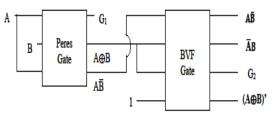

Figure 14: 1-Bit Comparator using CNOT, Peres and BJN Gate

The optimized design can be illustrated by:

Figure 15: Optimized 1-Bit Comparator

It can now be inferred from the above two figures, Figure 14 and Figure 15 respectively, that the design as well as the circuit complexity, the Quantum Cost, are reduced extensively; thus making the optimized model efficient in overall terms.

Thedifferences are now clearly tabulated below:

Table 10: Comparison of Different Designs of 1-Bit Comparator

| PARAMETERS                       | Figure 14 | Figure 15 |

|----------------------------------|-----------|-----------|

| Garbage Outputs                  | 2         | 2         |

| Logic Gates Used                 | 3         | 2         |

| Constant Ancillary Inputs Number | 3         | 1         |

| Quantum Cost                     | 10 6      |           |

| Improvement in Quantum Cost      | +40%      |           |

#### IV. CONCLUSION

It's now clear from the above design methodologies how Reversible Logic has redefined the way and the approach in which the Logical and Arithmetic Units were taken into consideration and designed using the conventional combinational logic techniques.

The paper has precisely brought into light the much hyped and unexplored world of Reversible Logic in the area of **Digital Electronics.**

The optimized models and the comparative analytical tables which employed the techniques of Reversible Logic have shown how the proposed designs have made the basic logical units economical and justifiable.

# REFERENCES

- Divyansh Mathur, Arti Saxena, Abneesh Saxena, "Arithmetic and 1. Logic Unit Designing using Reversible Logic Gate", International Journal of Recent Technology and Engineering, Volume 1, Issue 6, pp. 157-160, January 2013.

- 2. Himanshu Thapliyal and Nagarajan Ranganathan, "Design of Efficient Reversible Binary SubtractersBased on A New Reversible Gate", IEEE Computer Society Annual Symposium on VLSI, pp. 229-234, 2009.

- Himanshu Thapliyal and Nagarajan Ranganathan, "A New Design of 3. the Reversible Subtracter Circuit", 11thIEEE International Conference on Nanotechnology, pp. 1430-1435, August 2011.

- A.N. Al-Rabadi, "Reversible Logic Synthesis: FromFundamentals to 4. Quantum Computing", Springer Verlag, New York, First Edition, 2004.

- V. Vedral, A. Bareno and A. Ekert, "QuantumNetworks for 5. Elementary Arithmetic Operations". arXiv:quant-ph/9511018 v1. (November 1995)

- H. Thapliyal and N. Ranganathan, "Reversible LogicBased 6. Concurrently Testable Latches for MolecularQCA", To appear IEEE Trans. on Nanotechnology, 2009.

- 7. H. Thapliyal and N. Ranganathan, "Testable ReversibleLatches for Molecular QCA", Proc. of the 8th Intl. Conf. on Nanotechnology, Arlington, TX, Aug 2008, pp. 699-702.

- 8 H. Thapliyal and N. Ranganathan, "Conservative QCA Gate (CQCA) for Designing Concurrently Testable Molecular QCA Circuits", Proc. of the 22nd Intl. Conf. on VLSI Design, New Delhi, India, Jan 2009, pp. 511-516.

- X. Ma, J. Huang, C. Metra, F.Lombardi, "Reversible Gates and 9. Testability of One Dimensional Arrays of Molecular QCA", Springer Journal of Electronic Testing, Vol. 24, No. 1-3, pp.297-311, Jan 2008.

- 10. V. V. Shende, A. K. Prasad, I. L. Markov, and J. P. Hayes, "Reversible Logic Circuit Synthesis", InICCAD, San Jose, California, USA, pp. 125-132, 2002.

- 11. A C H Bennett, (1973) "Logical Reversibility of Computation", IBM Journal of Research and Development, vol. 17, no. 6, pp. 525-532.

- T. Toffoli, "Reversible Computing", Tech Memo MIT/LCS/TM-151, MIT Lab for Comp. Sci., 1980.

- 13. E. Fredkin, T. Toffoli, "Conservative Logic", Intl. Journal of Theoretical Physics, pp. 219-253,1982.

- 14. A. Peres, "Reversible Logic and Quantum Computers", Phys. Rev., pp. 3266-3276, 1985.

- 15. R. Feynman, "Quantum Mechanical Computers", Optic News, Vol. 11, pp. 11-20, 1985.

- 16. Md. Saiful Islam, Md. Rafiqul Islam, Muhammad Rezaul Karim and Abdullah Al Mahmud,"Synthesis of Adder Circuits using Reversible Logic", In Proc. of 3rd IEEE InternationalConference for Upcoming Engineers, ICUE 2004, Ryerson University, Toronto, Canada, May 13-14.2004.

- 17. Md. Saiful Islam, Md. Rafiqul Islam, Muhammad Rezaul Karim, Abdullah Al Mahmud and HafizMd. Hasan Babu, "Minimization of Adder Circuits and Variable Block Carry Skip Logic usingReversible Gates", In Proc. of 7th International Conference on Computer and InformationTechnology, ICCIT 2004, Brac University, Dhaka, Bangladesh, 26-28 December, 2004, pp. 378-383.

- 18. Md. Saiful Islam, Md. Rafiqul Islam, Muhammad Rezaul Karim, Abdullah Al Mahmud and HafizMd. Hasan Babu, "Variable Block Carry Skip Logic using Reversible Gates", In Proc. of 10th International Symposium on Integrated Circuits, Devices & Systems, ISIC 2004, NanyangTechnological University, Suntec, Singapore, 8-10 September, 2004, pp 9-12.

- 19. Md. Saiful Islam and Md. Rafiqul Islam, "Minimization of Reversible Adder Circuits", AsianJournal of Information Technology, Vol. 4, No. 12, pp. 1146-1151, 2005.

# **AUTHORS PROFILE**

Divyansh Mathur, scholar IVth year, Department of Electronics and Communication, Pranveer Singh Institute of Technology - College of Engineering, Kanpur.

Paper published: "Arithmetic and Logic Unit Designing using Reversible Logic Gate".

Prachi Singh, scholar IVth year, Department of Electronics and Communication, Pranveer Singh Institute of Technology - College of Engineering, Kanpur.

Dr. Sunita Singh, Assistant Professor, Department of Applied Sciences, Pranveer Singh Institute of Technology, Kanpur.

The author had obtained her Degree of Doctor of Philosophy from Harcourt Butler Technological Institute, Kanpur.

Furthermore, the author owns the publication rights of book, "A Textbook of Nanotechnology".

Published By:

& Sciences Publication