# Design and Synthesis of Reversible Fault Tolerant Carry Skip Adder/Subtractor

Prashanth. N. G, Manojkumar. S. B, Balaji. B. S, Naveena Pai G, Havyas. V. B

Abstract— Reversible logic will be having more demand in future computation technology because of its zero power dissipation under ideal conditions. This paper proposes the fault tolerant carry skip adder/subtractor by using parity preserving reversible logic gates. According to the control logic input the proposed design can works as a carry skip adder or carry skip subtractor.

Index Terms—Reversible Logic Gates, Parity Preserving reversible Logic Gates, Full Adder/Subtractor, Parallel Adder/Subtractor, Carry Skip Adder/Subtractor

#### I. INTRODUCTION

According to R Landauer [1] the traditional irreversible logic circuits i.e. made up by using conventional logic gates such as AND, OR, EX-OR etc. will generates a energy dissipation of kTln2 joules of energy for one bit of information to be lost during computation process. Where k is Boltzmann's constant =  $1.38 \times 10^{-23}$  J, T is absolute temperature at which computation process has been performed. The energy dissipation for one bit loss is a small value but this value can cause overheating in the circuit that will gradually decrease the life span of the circuit or device. C. H. Bennet [2] has shown that we can achieve zero power dissipation if the circuits are constructed using reversible logic gates. This paper proposes the design of fault tolerant carry skip adder/subtractor using parity preserving reversible logic gates. Fault tolerance is the property that will enables the system to continue its operation when the failure occurs in any one of the component. The faults or errors can also be find out by parity checking. In reversible logic fault tolerant circuits are constructed by using parity preserving reversible logic gates. A parity preserving reversible logic gate is the one in which input parity will matches with the output parity.

#### Manuscript received June 2013

**Prashanth.N.G**, PG Student, VLSI Design and Embedded System, B.G.S. Institute of Technology, B.G.Nagar, Mandya-571448, Karnataka, India.

Manojkumar.S.B, Assistant Professor, Department of Electronics and Communication Engineering, B.G.S. Institute of Technology, B.G.Nagar, Mandya-571448, Karnataka, India.

**Balaji.B.S**, Assistant Professor, Department of Electronics and Communication Engineering, B.G.S. Institute of Technology, B.G.Nagar, Mandya-571448, Karnataka, India.

Naveena Pai G, PG Student, VLSI Design and Embedded System, B.G.S. Institute of Technology, B.G.Nagar, Mandya-571448, Karnataka, India.

Havyas.V.B, PG Student, VLSI Design and Embedded System, B.G.S. Institute of Technology, B.G.Nagar, Mandya-571448, Karnataka, India.

#### **II. REVERSIBLE LOGIC GATES**

A reversible logic gate will be having equal number of inputs and equal numbers of outputs, and the inputs are easily retrievable from the outputs. A basic reversible gate will be having k inputs k outputs therefore it will be called as k\*k gate. In reversible logic gates fan out are not more than one and also no feedback paths are allowed.

#### III. PARITY PRESERVING REVERSIBLE LOGIC GATES

A reversible gate is parity preserving gate when its input parity will matches with output parity i.e EX-OR of all input will matches with EX-OR of all output [3]. Parity preserving reversible logic gates are the basic building blocks fault tolerant reversible circuits. There are several parity preserving reversible logic gates has been proposed in the literature. Feynman double gate (F2G) [4], Ferdkin gate (FRG) [5], Islam gate (IG) [6], Modified Islam gate (MIG) [7] and New Fault Tolerant gates (NFT) [8] are few among them.

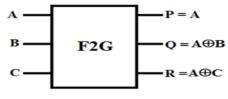

#### A. Feynman Double Gate (F2G)

It is a 3\*3 gate with input vector I(A,B,C) and output vector  $O(P=A, Q=A \oplus B, R=A \oplus C)$ . It will be having quantum cost of two. The Figure 1 shows the diagram of Feynman Double Gate.

Figure 1 Feynman Double Gate (F2G)

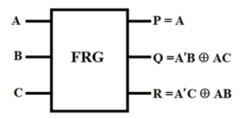

### B. Fredkin Gate (FRG)

It is a 3\*3 gate with input vector I(A,B,C) and output vector  $O(P=A, Q=A'B \oplus AC, R=A'C \oplus AB)$ . It will be having quantum cost of five. The Figure 2 shows the diagram of Fredkin Gate.

Figure 2 Fredkin Gate (FRG)

Published By: Blue Eyes Intelligence Engineering & Sciences Publication

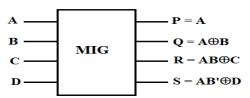

# C. Modified Islam Gate (MIG)

It is a 4\*4 gate with input vector I(A,B,C,D) and output vector O(P=A, Q=A  $\oplus$  B, R=AB  $\oplus$  C, S=AB'  $\oplus$  D). It will be having quantum cost of seven. The Figure 3 shows the diagram of Fredkin Gate.

Figure 3 Modified Islam Gate (MIG)

### **IV. PROPOSED WORK**

#### A. Fault Tolerant Full Adder/Subtractor

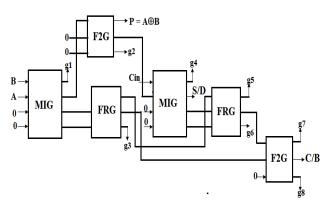

The Figure 4 shows the proposed fault tolerant full adder/subtractor. It can be designed using two MIG, two Feynman double gate and two Fredkin gate.

Figure 4 Proposed Fault Tolerant Full Adder/Subtractor (FT\_FA/S\_P)

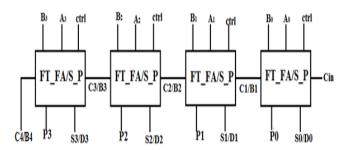

#### B. Fault Tolerant Parallel Adder/Subtractor

The basic building block of parallel adder/subtractor is full adder/subtractor. The Figure 5 shows the proposed 4-bit Fault Tolerant Parallel adder/subtractor, it can constructed using 4 fault tolerant Full Adder/Subtractor with propagate (FT\_FA/S\_P). The proposed design will work singly a unit which consists of both parallel adder and parallel subtractor. The design will consists of control line ctrl which will selects adder or subtractor according the control logic input i.e. when ctrl is 0 it will acts as parallel adder and when ctrl is 1 it will acts as parallel subtractor [9].

Figure 5 Proposed Fault Tolerant 4-Bit Parallel Adder/Subtractor

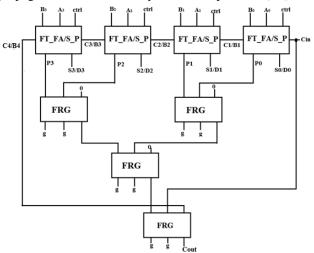

#### C. Fault Tolerant Carry Skip Adder/Subtractor

In the carry skip adder, delay is reduced due to the carry computation. In the full adder/subtractor operation, if either input is a logical one, the cell will propagate the carry/borrow input to its carry/borrow output. Hence, the nth full adder/subtractor carry/borrow input (C/B)n, will propagate to its carry/borrow output, (C/B)n+1, when  $P_n = A \oplus B$ . In addition, the multiple full adders/subtractors, making a block can generate a "block" propagate signal P to detour the incoming carry/borrow around to the block's carry/borrow output signal. Figure 6 shows the proposed four bit fault tolerant carry skip adder/subtractor block. It is quickly determined by each block, that whether the block's carry/borrow input is propagated to its carry output. If the block propagate P is one, the block carry/borrow input Cout [10].

Figure 6 Proposed Fault Tolerant 4-Bit Carry Skip Adder/Subtractor

#### V. SIMULATION RESULTS

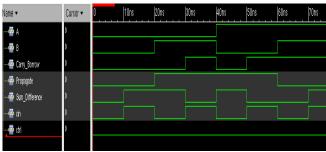

The entire architecture is modeled using Verilog language. The coding is done on Cadence Virtuoso tool and simulation is done on cadence SimVision tool. The Figure 7 and Figure 8 shows simulation results of proposed fault tolerant full adder and full subtractor, Figure 9 and Figure 10 shows simulation results of proposed fault tolerant 4-bit parallel adder and parallel subtractor and Figure 11 and Figure 12 shows simulation results of proposed fault tolerant 4-bit carry skip adder and carry skip subtractor respectively.

Figure 7 Simulation result of proposed fault tolerant full adder

Blue Eyes Intelligence Engineering & Sciences Publication

Published By:

Figure 8 Simulation result of proposed fault tolerant full subtractor

| Name 🔻                  | Cursor 🔻 | 0 | 10ns | 20ns | . 30ns |

|-------------------------|----------|---|------|------|--------|

| ⊕-¶a A(3:0)             | 'd 5     | 0 | 2    | 5    | 6      |

| ⊕-¶a 8(3:0)             | 'a 3     | 0 | 4    | 2    | 9      |

| 🔤 Carry_Borrow          | 0        |   |      |      |        |

| 🕀 👘 Propagate(3:0)      | 'd 6     | 0 | 6    | 1    | 15     |

| 🗄 🔞 Sum_Difference(3:0) | 'd 8     | 0 | 6    | 1    | 15     |

| 🜆 cin                   | 0        |   |      |      |        |

|                         | 0        |   |      |      |        |

Figure 9 Simulation result of proposed fault tolerant 4-bit parallel adder

| Name 🔻                  | Cursor 🔻 | 0 | 10ns | 20ns     | 30ns |

|-------------------------|----------|---|------|----------|------|

|                         | 'h 5     | 0 | 2    | 5        | 6    |

| <b>⊞¶a</b> B(3:0)       | 'h 3     | 0 | 4    | 2        | 9    |

| 🔤 Carry_Borrow          | 0        |   |      |          |      |

| ⊕-¶aropagate[3:0]       | 'h 6     | 0 | ) 6  | 7        | F    |

| ⊕ 🚋 Sum_Difference[3:0] | 'h 2     | 0 | E    | 3        | D    |

| 🖾 • cin                 | 0        |   |      |          |      |

| tti                     | 1        |   |      | 0 14 4 1 |      |

Figure 10 Simulation result of proposed fault tolerant 4-bit parallel subtractor

| Name 🕶              | Cursor 🔻 | 0 | 10ns | 20ns | 30ns |

|---------------------|----------|---|------|------|------|

| <b>⊡</b> -¶a A[3:0] | 'h 4     | 0 | 2    | 3    | 1    |

| ⊕-¶a B[3:0]         | 'h 5     | 0 | 4    | 6    | 2    |

| Cout                | 0        |   |      |      |      |

| 🕀 🕼 Sm_Df(3:0)      | 'h 9     | 0 | 6    | 9    | 3    |

|                     | 0        |   |      |      |      |

|                     | 0        |   |      |      |      |

Figure 11 Simulation result of proposed fault tolerant 4-bit carry skip adder

| Name 🕶              | Cursor 🔻 | 0 | 10ns | 20ns | 30ns |

|---------------------|----------|---|------|------|------|

| <b>⊕-√</b> 5 A(3:0) | 'd 0     | 0 | 2    | 3    | 1    |

| <b>⊡-√</b> B(3:0)   | 'd 0     | 0 | 4    | 6    | 2    |

| 🖾 Cout              | 0        |   |      |      |      |

| ⊞ 🔞 Sm_Df(3:0)      | 'd 0     | 0 | 14   | 13   | 15   |

|                     | 0        |   |      |      |      |

|                     | 1        |   |      |      |      |

Figure 12 Simulation result of proposed fault tolerant 4-bit carry skip subtractor

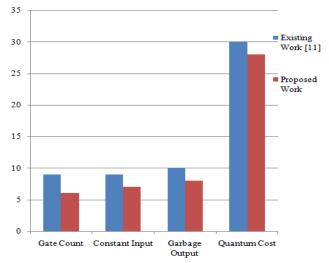

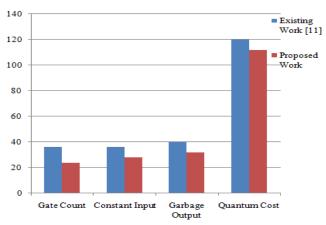

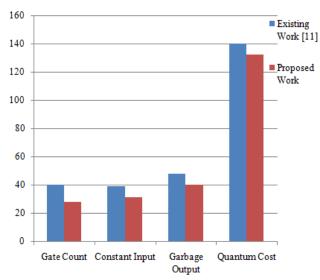

Table 1, Table 2 and Table 3 shows the comparative results of different fault tolerant Full Adder/Subtractor, 4-Bit Parallel Adder/Subtractor and 4-Bit Carry Skip Adder/Subtractor

**Table 1 Comparative Results of Different Fault Tolerant Full Adder/Subtractor**

| 04001                 |               |                   |                   |                 |  |

|-----------------------|---------------|-------------------|-------------------|-----------------|--|

|                       | Gate<br>Count | Constant<br>Input | Garbage<br>Output | Quantum<br>Cost |  |

| Existing<br>Work [11] | 9             | 9                 | 10                | 30              |  |

| Proposed<br>Work      | 6             | 7                 | 8                 | 28              |  |

Figure 13 Graphical representation of comparison of different fault tolerant full adder/subtractor

**Table 2 Comparative Results of Different Fault Tolerant** 4-Bit Parallel Adder/Subtractor

|                       | Gate<br>Count | Constant<br>Input | Garbage<br>Output | Quantum<br>Cost |

|-----------------------|---------------|-------------------|-------------------|-----------------|

| Existing<br>Work [11] | 36            | 36                | 40                | 120             |

| Proposed<br>Work      | 24            | 28                | 32                | 112             |

Figure 14 Graphical representation of comparison of different fault tolerant 4-bit parallel adder/subtractor

| Table 3 Comparative Results of Different Fault Tolerant |  |  |  |  |  |

|---------------------------------------------------------|--|--|--|--|--|

| 4-Bit Carry Skip Adder/Subtractor                       |  |  |  |  |  |

|                       | Gate<br>Count | Constant<br>Input | Garbage<br>Output | Quantum<br>Cost |

|-----------------------|---------------|-------------------|-------------------|-----------------|

| Existing<br>Work [11] | 40            | 39                | 48                | 140             |

| Proposed<br>Work      | 28            | 31                | 40                | 132             |

Published By:

& Sciences Publication

Figure 15 Graphical representation of comparison of different fault tolerant 4-bit carry skip adder/subtractor

# VI. CONCLUSION AND FUTURE WORK

This paper presents efficient approach for the design of fault tolerant carry skip adder/subtractor. The proposed design can work as single unit that can acts as carry skip adder as well as carry skip subtractor depending upon our requirement. The proposed design offers less hardware complexity, less gate count, less garbage bits and constant inputs.

In future we are planning to design more optimized or efficient Fault tolerant carry skip adder/subtractor design i.e. less garbage bits and constant input, gate count and quantum cost.

### REFERENCES

- R. Landauer, "Irreversibility and Heat Generation in the Computational 1. Process", IBM Journal of Research and Development, 5, pp. 183-191, 1961

- C.H. Bennett, "Logical Reversibility of Computation", IBM J. Research 2. and Development, pp. 525-532, November 1973.

- B. Parhami, "Fault tolerant reversible circuits", in Proceedings of 40th 3. Asimolar Conf. Signals, Systems, and Computers, Pacific Grove, CA, pp. 1726-1729, October 2006.

- E. Fredkin and T. Toffoli, "Conservative logic", Intl. Journal of 4 Theoretical Physics, pp. 219-253, 1982. B.

- R. Feynman, "Quantum mechanical computers", Optical News, vol. 11, 5 1985, pp. 11-20.

- M. S. Islam, M. M. Rahman, Z. Begum, M. Z. Hafiz and A. A. Mahmud, 6. "Synthesis of fault tolerant reversible logic circuits", In Proc. IEEE International Conference on Testing and Diagnosis, Chengdu, China, 28-29 April, 2009.

- Islam S. and M. Mahbubur Rahman, 2009b. "Efficient Approaches for 7. Designing Fault Tolerant Reversible Carry Look-Ahead and Carry-Skip Adders", MASAUM Journal of Basic and Applied Sciences, 1(3): 354-360.

- Majid Haghparast and Keivan Navi, "A Novel Fault Tolerant Reversible 8. Gate For Nanotechnology Based Systems", American Journal of Applied Sciences 5 (5): 519-523, 2008 ISSN 1546-9239

- 9. Prashanth N G, Savitha A P, M.B.Anandaraju, Nuthan A C, "Design and Synthesis of Fault Tolerant Full Adder/Subtractor using Reversible Logic Gates". International Journal of Engineering Research and Applications (IJERA) ISSN: 2248-9622 Vol. 3, Issue 4, Jul-Aug 2013 pp137-142

- 10. Himanshu Thapliyal, M.B Srinivas, "A New Reversible TSG Gate and Its Application for Designing Efficient Adder Circuits" arXiv preprint cs/0603091, 2006

- Parminder Kaur & Balwinder singh Dhaliwal "Design of Fault Tolerant 11. Full Adder/Subtractor Using Reversible Gates" 2012 International

Conference on Computer Communication and Informatics (ICCCI -2012), Jan. 10 - 12, 2012, Coimbatore, INDIA

Prashanth.N.G obtained his BE

Management, Bhatkal, Karnataka in

2011. Currently he is pursuing M.Tech in VLSI Design and

Embedded System in B.G.S. Institute of technology, B.G.Nagar, Mandya,

Manojkumar.S.B obtained his

Communication from Shridevi Institute

of Technology, Tumkur, Karnataka in

2006 and his M.Tech in VLSI Design and Embedded System from PES College of

Engineering, Mandya, Karnataka in

2009. He is currently working as Assistant Professor in Department of

and

B.G.S.

B.G.Nagar,

in

in

of

Communication

Electronics

Technology

Electronics

from Anjuman

and

and

BE

and

of

Mandya,

Communication

Institute

# **AUTHORS PROFILE**

degree

Institute

Karnataka.

degree

Electronics

Engineering.

Technology,

Karnataka.

Balaji.B.S obtained his BE degree in Electronics and Communication from

Naveena Pai G obtained his BE degree in Electronics and Communication from B.G.S. Institute of technology, B.G.Nagar, Mandya, Karnataka in 2009. Currently he is pursuing M.Tech in VLSI Design and Embedded System in B.G.S. Institute of technology, B.G.Nagar, Mandya, Karnataka.

Havyas.V.B obtained his BE degree in Electronics and Communication from Adichunchanagiri Institute of Technology, Chikamagalur, Karnataka in 2011. Currently he is pursuing M.Tech in VLSI Design and Embedded System in BGS Institute of technology, B.G.Nagar, Mandya, Karnataka.