# Efficient Speed Control of 3-ph Induction Motor with Two Stage IPFC Using 1-ph Supply

# Kushal Dhawad, R. D. Patane, Vittesh Naphade

Abstract— Today in industry, 3-ph IM are being used at very wide scale. So its speed control according to specific requirement is very important. Also many times, 3-ph IM are to be operated with easily available 1-ph supply. For this, proposed mechanism of improving input power factor here is very efficient and reliable. At input terminal, high performance Two Stage Interleaved Power Factor Correction technique (IPFC) with boost topology operating with discontinuous current conduction is used. With this circuit, 3<sup>rd</sup> order harmonics can be eliminated upto completely from the input supply. Also it will help to achieve almost UNITY pf with rated power supply. With this type of 3-ph supply provided to the IM, Reactive power generation can be minimised which leads to efficient control over the wastage of Reactive power and use of Reactive power compensation techniques. So the overall cost of operating 3-ph IM can be minimised.

Index Terms— Two stage Boost topology, Discontinuous current conduction, IPFC, Sine-wave PWM, 3-ph bridge Inverter.

## I. INTRODUCTION

Today in industries, the speed of induction motor can be effectively controlled by V/f method. By maintaining V/f ratio constant throughout the operation, this controlling can be achieved. But problem still persist with power factor correction. Active PFC is said to be better method for this. But it is not possible to improve input power factor to the desired level of efficiency with APFC.

So another improved method for power factor correction is stated here known as Interleaved Power Factor Correction (IPFC).

With this method, nearly Unity power factor can be achieved which helps in reducing the 3<sup>rd</sup> Order Harmonics. The 3<sup>rd</sup> order harmonics are mainly responsible for reduction in the overall efficiency of the Induction Motor by introducing ripples in the input supply. With the input supply, as elimination of higher order harmonics can be easily done with the help of filter so we just concentrate on the methodologies to be adopted for the removal of 3<sup>rd</sup> order harmonics completely from the supply. For this, the IPFC can be the best suited method because it helps in removing ripples due to 3<sup>rd</sup> harmonics completely from the input supply. As 3<sup>rd</sup> order harmonics are eliminated it will help improving input power factor become almost UNITY.

#### **II. OBJECTIVE**

As we know Converters are the best option for situations where three phase AC supply is not available, advanced Sine-PWM techniques are employed to achieve output voltage with minimum distortion.

#### Manuscript received February 15, 2014.

Kushal G. Dhawad He is working as Assistant Professor in the department of Electrical Engineering in Lokamanya Tilak College of Engineering, Koparkhairane, Navi Mumbai, India.

R.D. Patane, He is working as Asso Professor & HOD in the department of General Engineering in Terna Engineering, Nerul, Navi Mumbai, India.

Vittesh Naphade, He is working as Assistant Professor in department of Electrical Engineering in Lokamanya Tilak College of Engineering, Koparkhairane, Navi Mumbai, India.

In this paper, we are introducing a new technique Two-stage IPFC (Interleaved power factor correction) to improve the quality of input power supply. Thus giving maximum efficiency for the 3-phase Induction Motor. The proposed IPFC technique for effective controlling of motor used here gives improved input current with almost 100% reduction of harmonics.

With this method, as the input current is optimised at supply side only therefore the use of filter circuit will be eliminated which will reduce overall cost of operation and speed control of the 3-phase IM. The function of filter stage and PFC (Power Factor Correction) stage will be performed by IPFC stage alone. Therefore the space required for the mounting of the circuit will be less. Hence, this method will be more efficient than all other existing methods.

# **III. INTERLEAVED POWER FACTOR** CORRECTION

Interleaved Power Factor Correction (IPFC) stage improves the input power factor by reducing significance of mainly 3<sup>rd</sup> order harmonics. Without such a PFC stage, the current drawn will have significant harmonic contents which in turn will result in increased network losses, radiated emission and total harmonic distortion(THD). At higher power levels, these problems become more pronounced, thereby reducing overall efficiency of the system.

The aim of IPFC is to provide resistive input impedance, means the input power factor must be close to UNITY. This allows maximum use of active power thus reducing the generation and hence wastage of reactive power. Therefore the problem of use of reactive power compensation technique is also eliminated.

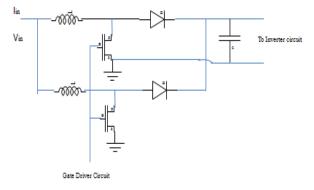

Fig 1. Interleaved power factor correction.

This type of distribution can be achieved by selecting proper magnitude of Inductance of the boost converter. The output from this stage will then be added together to get ripple free supply. This will eliminate the need for filter circuit to be used. Thus the output of two stage interleaved power factor correction circuit will be at approximately UNITY power factor.

Retrieval Number: D0657022414/2014©BEIESP

Published By:

& Sciences Publication

This output current from IPFC circuit will then fed to 3-phase IM via 3-phase bridge inverter circuit. This improved input supply will improve the speed controlling and hence its efficiency up to 98%. With the existing control techniques this efficiency will never go beyond 95%.

With such PFC, the reactive power generation will be negligible. This will also minimize the cost of reactive power compensation circuitry. Thus the overall cost for speed control reduces and efficiency of the 3-phase induction motor used will increase because of the reduction in harmonics by achieving UNITY power factor.

#### **IV. INTERLEAVED BOOST TOPOLOGY:**

In the IPFC technique explained above, two boost circuit are arranged in parallel connection. The two inductors in parallel will share total load equally. And by providing proper switching signals to MOSFET, the desired magnitude of supply will be provided to the inverter section.

The interleaved boost topology is so arranged as two boost converter circuit connected in parallel operating  $180^{\circ}$  out of phase in discontinuous conduction mode of operation. The input current is the sum of the two inductor branch currents IL1 and IL2. Because the inductor's ripple currents are  $180^{\circ}$ out of phase, they will cancel out each other and reduces the input ripple current through the inductors.

The best input inductor ripple current cancellation can be achieved at 50% duty cycle, which means input supply must be shared by both inductors equally. The current across output capacitor will be, ICout = (I1 + I2 - Iout). Where Iout is the output current. Interleaving reduces the output capacitor ripple current (IOUT) as a function of duty cycle.

#### V. PULSE WIDTH MODULATION:

The efficient method of controlling the output voltage is to incorporate PWM techniques within the inverter. This technique also helps in reducing the harmonics if remained after IPFC stage in the output voltage. Commonly used PWM techniques are -

- 1. Single pulse modulation.

- 2. Multiple pulse modulation.

- 3. Sinusoidal pulse modulation

Sinusoidal PWM is most used and trusted method in industries. One of the major issues with PWM is the presence of harmonics. The higher order harmonics around the carrier frequency are relatively easier to filter out, but the lower order harmonics smaller in magnitude cause problems for the PWM inverters. To reduce these lower order harmonics a variety of techniques have been proposed. Sinusoidal pulse width modulation (SPWM) technique is used to generate gate pulses. SPWM is a very simple technique for harmonic reduction. In this technique pulse magnitude will be constant and only pulse width can be changed. In this pure sine wave is compared with triangular wave for producing gate pulses.

# VI. V/F CONTROL METHODOLOGY

Induction motor control is complex due to its nonlinear characteristics. While there are different methods for control, Variable Voltage Variable Frequency (VVVF) or V/f is the most common method of speed control in open loop. This method is most suitable for applications without position control requirements or the need for high accuracy of speed control. The frequency and speed of the motor, with respect to the input supply, is called the synchronous frequency and synchronous speed. Synchronous speed is directly proportional to the ratio of supply frequency and number of poles in the motor. Synchronous speed of an induction motor is shown in Eqn.

Synchronous Speed (Ns) = (120 x f) / P

Synchronous speed is the speed at which the stator flux rotates. Rotor flux rotates slower than synchronous speed by the slip speed. This speed is called the base speed. The speed listed on the motor nameplate is the base speed.

Base Speed N = Synchronous Speed – Slip Speed

Percent Slip = [(Synchronous Speed – Base Speed) x 100]/ Synchronous Speed.

By maintaining V/f ratio constant throughout the operation of motor, efficient control of motor can be achieved. One can vary either voltage or frequency of the supply in order to control the speed of induction motor to be used.

#### VII. EQUATIONS

## A. V/f control technique:

Stator Voltage (V)  $\propto$  [Stator Flux ( $\phi$ )] x [Angular Velocity ( $\Phi$ )]

$V \varpropto \Phi \ge 2\pi f$

$\Phi \varpropto V/f$

# **B.** Duty Cycle for Interleaved Boost topology:

D= 1- [Vin (min) x  $\eta$ ] / Vout

Vin (min) = minimum input voltage

Vout = desired output voltage

$\eta = efficiency of the converter$

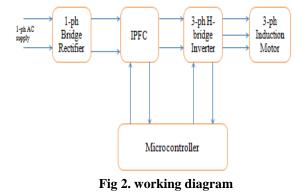

# VIII. WORKING

The circuit diagram of the operation is given below:

The circuit is schematic of implemented speed control of 3- phase induction motor using single phase supply along with interleaved power factor improvement is as shown in Fig. The circuit diagram can be divided into three parts. Part 1 consists of diode bridge rectifier. This circuit will convert the 1-phase AC supply into DC output with some distortions. This output can be termed as sinusoidal DC output. It will then be fed to the two stage interleaved power factor correction circuit which is the second part of this circuit. In this circuit, the input power supply is divided equally among two boost branches. With the MOSFET operating at 50% duty cycle, the ripple occurring due to inductor current can be eliminated completely. So that pure DC supply can be given to the inverter circuit to be fed to the 3-phase induction motor operating as load.

The boost switch is turned ON at constant frequency with constant ON time. This is done with discontinuous mode of conduction. Since this switching frequency is usually very high (kHz), filtering of the unwanted input current harmonics becomes a relatively easy task and can be achieved with the help of a small input capacitor and inductor. Therefore the overall input power factor after filtering (i.e. at ac source) is very close to unity.

Part 3 represents three phase voltage source sine PWM inverter. POWER MOSFETS are being used as switching devices along with anti-parallel diodes.

The boosted dc voltage is connected to three phase induction motor through a three phase bridge inverter with a suitable control circuitry which changes the switching frequency of inverter from 20 to 25kHz which leads to the control of the frequency and the output of inverter from 0 to 50Hz. For Continuously variable speed control, the output frequency of inverter must be varied. The applied voltage to the motor must also be varied in linear proportion to the supply frequency to maintain constant motor flux. At low frequency, where the motor inductive reactance is low, boosted voltage is used to compensate for the stator IR voltage drop. Thus control of both voltage and frequency is necessary for proper variable speed operation.

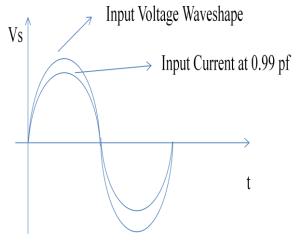

## **IX. EXPECTED RESULT**

The output of IPFC stage is expected to be the wave shape shown below.

# X. CONCLUSION

This IPFC converter for effective speed control of motor is most suitable for rural areas where 3-phase pump motors are to be operated with easily available 1-phase supply with reduced harmonics distortion and compensation of reactive power is also achieved. IPFC also improves input current with discontinuous conduction current. With the use of IPFC overall efficiency of the system can be improved by significant amount.

#### REFERENCES

- An Interleaving PFC Pre-Regulator for High-Power Converters: 1. Michael O'Loughlin, Texas Instruments.

- Speed Control of Three Phase Induction Motor using Single Phase 2 Supply along with Active Power Factor Correction: Sanjay L Kurkute,

Pradeep E &TC Dept., RSCOE, Pune (M.S.) INDIA, M Patil Electronics Dept. VIT, Pune (M.S.) INDIA

- Implementation of Modified Reference PWM for Reducing the 3. Harmonics in Inverters by using Matlab/Simulink: G.Sudha Rani1 ,Rasool Ahemmed.SK , N.Lavanya M.Tech Student, Dept. of EEE, KL University, Vaddeswaram, Guntur District, India Assistant Professor, Dept. of EEE, K L University, Vaddeswaram, Guntur District, India Research Scholar, Dept. of EEE, K L University, Vaddeswaram, Guntur District, India

- 4. Estimative Current Mode Control Technique for DC-DC Converters Operating in Discontinuous Conduction Mode: M. Ferdowsi, Student Member, IEEE, and A. Emadi, Senior Member, IEEE.

- 5. EE HomePage.com Powerpoint Symbol Collection Logic Elements.

- Understanding Boost Power Stages in Switchmode Power Supplies: 6. Everett Rogers, Texas Instruments,

- 7. CONTROL TECHNIQUES FOR POWER FACTOR CORRECTION CONVERTERS

- 8. \*L. Rossetto, \*\*G. Spiazzi, \*\*P. Tenti

- \*Department of Electrical Engineering 9.

- 10 \*\*Department of Electronics and Informatics University of Padova, Via Gradenigo 6/a, 35131 Padova – ITALY

- 11. Improving Efficiency & Reliability Using Interleaved Boundary Condition Mode Power Factor Correction by John Harper, Fairchild Semiconductor.

# **AUTHORS PROFILE**

Kushal G. Dhawad, was born in Nagpur, District Nagpur, Maharashtra, India on October 2, 1988. He received B.E (Electrical) degree in 2011 from Nagpur University, Nagpur, Maharashtra and pursuing M.E.(Electronics) from 2012 to 2014. He is a member IEEE. Research areas include power electronics, transmission of electricity both wired and wireless, non-conventional energy. He is working as Assistant Professor in the department of Electrical Engineering in Lokamanya Tilak College of Engineering, Koparkhairane, Navi Mumbai, India.

R.D. Patane, He is working as Asso Professor & HOD in the department of General Engineering in Terna Engineering, Nerul, Navi Mumbai, India.

Vittesh Naphade, He is working as Assistant Professor in department of Electrical Engineering in Lokamanya Tilak College of Engineering, Koparkhairane, Navi Mumbai, India.

Published By:

& Sciences Publication