# Design and Implementation of Real time ECG Circuit Based On FPGA

# Raaed Faleh Hassan, Safa Majed Mohammed

Abstract: The diagnosing of the heart abnormality can benefit from the availability of analyzing techniques for the electrocardiogram (ECG) signal. A system which is acquire ECG signal and extract the heart activity features has been designed and implemented in this paper. The implemented system includes four stages; signal acquiring stage, signal conditioning stage, transmission channel stage, and diagnosing stage. Three electrodes are placed on the left and right arm and left leg of the patient for acquiring ECG signal. The second stage is designed for the purpose of amplifying and filtering the acquired weak signal which is corrupted by noise from muscles and electrical source. The extracted analog ECG signal is converted to the digital signal in this stage also. In order to realize the functionality of this stage, instrumentation amplifier, high pass filter, notch filter, and low pass filter have been implemented to extracting analog ECG. Arduino is configured in this stage for converting the analog ECG signal into digital signal, it is also acts as a gateway to transfer the digital ECG to the transmission channel. Wireless transmission channel has been implemented based on Xbee located at both channel sides. Finally, the core of the diagnosing stage has been designed using Language VHDL language and implemented using Spartan 3AN XC3S700 FPGA Starter Kit board. The algorithm implemented in the diagnosing stage concerned with the detecting of R- peaks in ECG signal. According to a deviation in duration or amplitude of these peaks from the standard values, the diagnosing stage indicates one type of the heart abnormality which is appear at the LCD of FPGA. Experimental tests have been performed for different cases and show promising results toward precise diagnosis of heart irregular activities.

Keywords: ECG Circuit; Arduino; ZigBee; UART; VHDL; FPGA.

# I. INTRODUCTION

Electrocardiograph is the representation of the electrical potential of the heart. Physicians record ECG easily by attaching small electrodes to the human body. The heart is a muscle formed in a way that allows it to act as a pump for blood. ECG is a semi periodic repeating waveform that represent the function of the heart, which acts as a generator of bioelectric events [1]. The primary pacemaker of the heart is a group of cells which are known as Sino-Atrial (SA node) [1]. It is located in the posterior part of the right atrium at the junction of the superior vena cava [2]. The function of the SA node is to initiate the heart activity by generating impulses at the normal rate of the heart which is about 60-100 beat per minute for adult at rest. The impulses generated by SA node contracts the atrial muscle and this

Revised Version Manuscript Received on August 02, 2017.

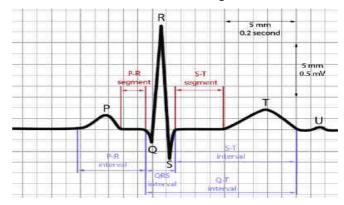

impulse spread through the atrial wall to the Atrio-Ventricular (AV) node which is located at the lower part between the two atria. AV node ensures that the ventricles contracted after the completion of the atria contraction. The standard ECG waveform is shown in Fig.1.

Fig. 1 A Typical ECG Signal

From Fig.1, the first deflection is the P wave which reflects depolarization of the atria. This is followed by the QRS complex which reflects depolarization of the ventricles and then the ST segment and T wave which reflect repolarization of the ventricles. The cause of the U wave remains unclear [2]. Table I shows the normal duration and amplitude for each part of ECG waveform.

**Table I: Normal ECG Parameters**

| Phase       | Duration<br>(Sec) | Amplitude<br>(Volt) |  |  |  |  |  |  |

|-------------|-------------------|---------------------|--|--|--|--|--|--|

| P Wave      | 0.06-0.11         | < 0.25              |  |  |  |  |  |  |

| PR Interval | 0.12-0.20         | -                   |  |  |  |  |  |  |

| PR Segment  | 0.08              | -                   |  |  |  |  |  |  |

| QRS Complex | < 0.12            | 0.8-1.2             |  |  |  |  |  |  |

| ST Segment  | 0.12              | -                   |  |  |  |  |  |  |

| QT Interval | 0.36-0.44         | -                   |  |  |  |  |  |  |

| T Wave      | 0.16              | <0.5                |  |  |  |  |  |  |

ECG signal feature extraction is the backbone of the heart activity analysis. Therefore, detection and analysis of this signal has attracted the attention of many researchers. Most of these researches focused on the analysis of the ECG data obtained from database systems [3] - [17]. Many of the algorithms have been explored and proposes toward the signal extraction and analysis.

**Dr. Raaed Faleh Hassan,** Department of Computer Engineering, Middle Technical University / Electrical Engineering Technical Collage / Organization Name, Baghdad, Iraq, E-mail: <u>drraaed@hotmail.com</u>

Safa Majed Mohammed, Department of Computer Engineering, Middle Technical University / Electrical Engineering Technical Collage / Organization Name, Baghdad, Iraq, E-mail: <u>Safa.Sufi33@gmail.com</u>

These algorithms distributed between the adoption of time domain analysis of the ECG signal approach [4, 5, 8, 10, 11, 15, 16, 17] and time – frequency transform approach [3, 6, 7, 9, 12, 13, 14]. In time domain approach, the features of ECG is compared with normal signal from an amplitude and duration points of view which detect the type of abnormality. In time-frequency transform approach, Discrete Wavelet Transform (DWT) has been employed for removing high frequency noise [9,13] and detecting the ECG features as well [3, 6, 7]. Least Mean Square (LMS) and FIR filter are combined with time domain analysis for denoising the ECG signal [12, 14].

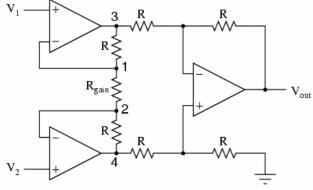

## **II. ECG CIRCUIT DESIGN AND IMPLEMENTATION**

As stated in the literature, ECG signal is the corner stone of diagnosing heart activity. Unfortunately, ECG is a weak electrical signal and suffers from distortion by different noise types. In order to accomplish the accurate diagnosis, a readable and noise - free ECG signal is needed. Therefore, the circuit that is designed to extract the ECG signal must ensure these requirements to achieve the remove noise effectively and protect the useful components of ECG signals [18].

the following charts and sequence were developed:

- 1. HPF was used to eliminate the base line wander.

- 2. notch filter was used to eliminate of power line noise [19].

- using LPF to remove noise of high frequency from the 3. signal.

- Amplify the ECG signal using the instrumentation 4. amplifier to increase the signal voltage level.

The required bandwidth for ECG signal(0.5Hz-30Hz) for normal heart human, so the bandwidth of the circuit has been chosen to be within this rang. Also, the gain should be enough to make the signal observable however, it should not be large enough to saturate the devices, so that no false peak should occur.

Based on these constraints, scheme of the ECG circuit is shown in Fig.2

Fig. 2: scheme of ECG circuit.

# A. Electrodes

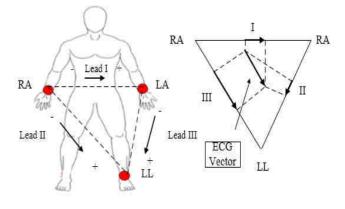

The first element in the ECG circuit is the electrodes. Electrode [20] is a transducer device that converts tissue

contractions into electrical voltages. Attached several electrodes to the patient's skin leads to the measuring of ECG signal. In this paper two electrodes are connected to the right and left arms, and the common electrode is connected to left leg as shown in Fig.3. The electrode produces an output voltage in the range of 2 - 3 mV.

Fig .3: A 3-lead connection.

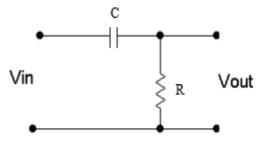

# B. High Pass Filter

The second element is HPF, the ECG signal passes through High Pass Filter to remove the base line wander. a RC filter (capacitor C and resistor R) configuration (Fig.4) [21].

Fig.4: High pass filter.

The cutoff frequency (fc) is 0.23 Hz and C was set to1µf. Therefore, the resistor R has the following value:

$$R = \frac{1}{2\pi f_c C} = \frac{1}{2\pi (0 \cdot 23)(1 \times 10^{-6})} = 680K\Omega$$

(1)

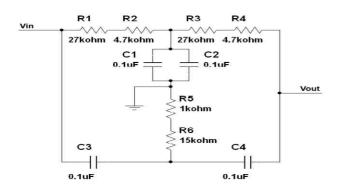

# C. Notch Filter

A notch filter is used to eliminate the effect of power line interference [22] which operates at 50Hz. therefore, the cutoff frequency (fc) for this filter is 50 Hz.

The twin T circuit is highly helpful as a notch filter. The twin T provides a large degree of refusal at the certain frequency. This notch filter can be helpful to remove unwanted signals on the certain frequency.

The response save by the filter consists of a low level of attenuation away from the frequency of notch.

As signals move closer to the frequency of notch, the level of attenuation rises, giving the typical notch filter

response. Theoretically, in the notch frequency the level of attenuation which offer by the twin, T notch filter is infinite. With fc = 50 Hz and  $C = 0.1 \mu F$ , the resistor value in this filter is:

$$R = \frac{1}{2\pi f_c C} = \frac{1}{2\pi (50)(1 \times 10^{-6})} = 31 \cdot 7K\Omega$$

(2)

The filter configuration with the real values is shown in Fig.5. Where, R = R1 + R2 = R3 + R4, R/2 = R5 + R6, C = C3 = C4 and 2C = C1 + C2

Published By:

Fig. 5: Twin-T Notch Filter (with real component values).

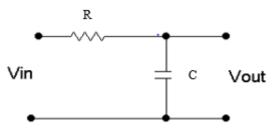

## D. Low Pass Filter

The ECG signal is outgoing from notch filter sent out to LPF to minimize the high frequency distortion that is generated by muscle activity which falls in a range of (30-2000Hz). The low pass filter [21] is shown in Fig. 6.

The cutoff frequency fc is 33.88 Hz and C was set to  $0.1\mu f$ . Thus, the resistor R has a value of:

$$R = \frac{1}{2\pi f_c C} = \frac{1}{2\pi (33 \cdot 88)(0 \cdot 1 \times 10^{-6})} = 47K\Omega \qquad (3)$$

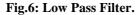

#### E. Instrumentation Amplifier

Many picked waveform is very small in its amplitude, therefore, the main challenge of this stage includes

amplifying the desired weak signal in the presence of noise from electrical sources and other muscles.

Many medical applications can have used instrumentation amplifiers to condition small signals in the presence of large common-mode voltages and DC potentials. Therefore, we choose Analog instrumentation amplifier to magnification the ECG voltage resulting from electrodes, which is in the range of 2mV to 3mV. in this project we used op-amp 741 to designed the instrumentation amplifier with power supply of +12V to -12V and gain of 201. Instrumentation amplifier as illustrative in Fig.7, it consists of three op-amps [23].

Fig.7: Instrumentation Amplifier.

The complete graph of ECG circuit is shown in Fig.8 and Fig.9 shows the hardware implementation of this

Fig .9: implemented circuit.

### **III. ADC MOUDLE**

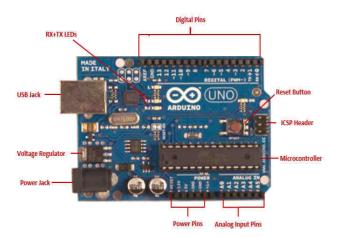

The Arduino that is used for this proposed system to convert ECG signal from analog to digital form and readability data by software programming sing integrated development environment (IDE) program. Arduino UNO which is shown in Fig.10 is a microcontroller based on ATMega328 which consists of14-digital pin entries, 16 MHz resonator, USB linkage, reset push button, power jack, and 6 channel with 10bit used for analog to digital converter. Also, the linear value from 0 to 1023 the interview 0V to +5V respectively [24].

The Arduino reads the analog input voltage (at input A0) from the ECG circuit and converts it to digital form thensends data to Spartan-3A/3AN FPGA Starter Kit Board via XBees module (S2). Arduino UNO possesses the necessary features to support the microcontroller by connecting it to the PC through USB cable with baud rate 19,200[25].

# Design and Implementation of Real time ECG Circuit Based On FPGA

Fig.10: Arduino Uno.

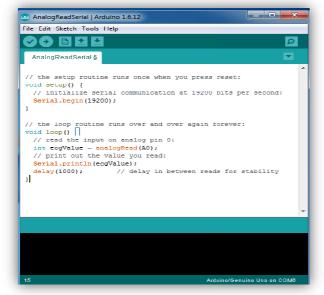

The following code show the Arduino Software (IDE) (can see Fig.11):

Fig.11: Arduino Uno Code

ECG signal which shows its output of the Arduino Serial plotter in Fig.12.

Fig.12: Output Signal from Arduino Uno.

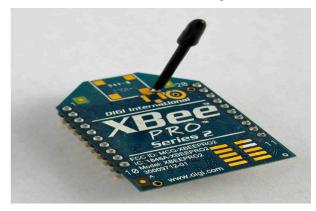

# **IV. ZIGBEE**

We choose wireless technology as a way to transmit data and used the ZigBee Series 2[26] for this purpose. First of all, there must be connection between the Arduino and the ZigBee. The ZigBee shield was used here to connect between them. For this research two ZigBee is expected to transmission information and accepting information for remote connection. First XBee module used as AT Router (TX) which connect with the Arduino Uno board via XBee shield, While the second XBee module used as AT Coordinator (RX) which Connect with USB adapter and connect it (at rx pin) with 6 pin Accessory Header (at V14 pin) in Spartan-3AN FPGA starter kit.

XCTU is a tool to configure ZigBee modules. after then configure the Radio Frequencies which launches the XCTU software beneath computer setting via make sure the Baud Rate in 19200.

Fig. 13 show the ZigBee (XBee Pro S2) used for wireless transfer data between sender and receiver. Also, it is used in implementing applications which need prolonged battery life, low data rate, and safe networking.

The data transfer rate is 250 Kbps for the purpose of sending a single signal from the

input device or any sensor. The electrocardiogram (ECG) signal was send to FPGA via wireless communication. Designation the baud rate to 19200 for setting up connections between FPGA device and serial connections. Xilinx software will show the result through LCD in FPGA.

Fig.13: ZigBee/XBee Pro Series 2.

## V. IMPLMENTION HARDWARE

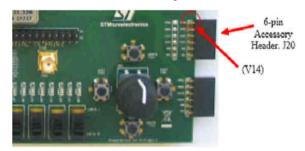

Xilinx ISE Design 14.5 is a software tool used to perform the program on FPGA using Language (VHDL). in this project, the Spartan3AN XC3S700 FPGA Starter Kit board uses. after The FPGA receives the data from Arduino via ZigBee S2 by V14 pin (6 pin Accessory Header in Spartan-3AN FPGA starter kit shown in Fig.14.

Fig.14: 6-pin Accessory Header, J20.

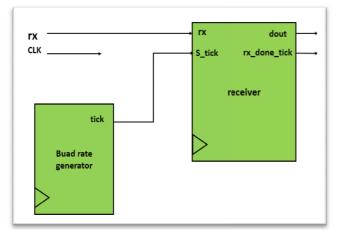

UART receiving subsystem (can see in Fig.15) used only to receive data at V14 pin and set the sampling rate must be  $19200 \times 16$  which equal to

Published By: Blue Eyes Intelligence Engineering & Sciences Publication Pvt. Ltd.

307200 Ticks Per Second.

Fig.15: diagram of receiving subsystem for UART.

The clock rate is 50 MHz for the system, So it requires baud rate generator mod 163  $\left(\frac{50 \times 10^6}{307200}\right)$  counter. Therefore, confirmation the cycle tick for one clock once all 163 clocks cycles [27]. after the data has been received correctly, the data is stored in RAM, which converts data from Hex to decimal values for easy handling. Then Xilinx ISE analysis the ECG signal values and diagnosis most of the abnormal activities of the heart.

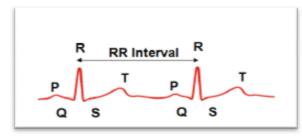

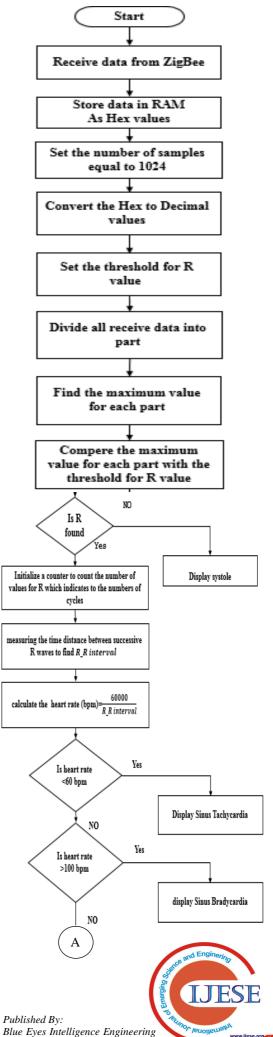

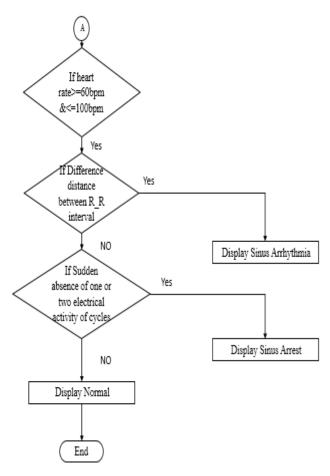

The (V14) pin receive data and store in RAM which receive data from XBee as hex and convert it to decimal value. Then, the Xilinx ISE analysis the ECG signal values and diagnosis most of the abnormal activities of the heart. The flow chart showed in Fig.17 represents the algorithm for diagnosis the abnormal activities. The Xilinx ISE calculate the normal heart rate (calssically 60 to 100 bpm for an adult) from the equation:

Heart Rate (in bpm) =  $\frac{60,000}{R_R interval(in ms)}$ by measuring the time distance between successive R waves with a beat -to-beat variation in R-R interval[28].

Fig.16: R-R interval.

Table II shows the names of some abnormality and characteristics featuer for ECG signal.

# Table II: Abnormal state of ECG signal.

| S.No. | Name of Abnormality | Characteristic Features                           |

|-------|---------------------|---------------------------------------------------|

| 1     | Sinus Tachycardia   | Heart rate (R_R interval)>100bpm                  |

| 2     | Sinus Bradycardia   | Heart rate (R_R interval)<60bpm                   |

| 3     | Sinus Arrest        | A sudden absence of electrical activity of cycles |

| 4     | Sinus Arrhythmia    | Difference distance between R_R interval          |

| 5     | Asystole            | No electrical activity                            |

# Design and Implementation of Real time ECG Circuit Based On FPGA

# Fig.17: Flowchart of diagnosis system and calculate the heart rate.

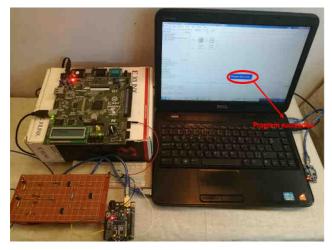

when finish from the downloading, FPGA displays results on LCD and LED as shown in Fig.18.

Fig.18: Spartan-3AN FPGA starter kit configuration.

# VI. RESULT

The Xilinx ISE (14.5) will analysis the ECG signal values and diagnosis most of heart irregular activities whether patient normal or abnormal.

The design implemented in hardware was tested using six data records obtained from the database maintained at the Physio Bank website. In this project was used 16 x 2 LCD and LED for displaying the results in the screen on the FPGA.

The results of simulating of normal ECG signal can show in Fig.19.

| Name          | Value    | 1.6256 | 556 ms | 558 ms       | 560 ms | 562 ms          | 564 ms               | 566 ms     | 568 ms | 570 ms         | 572 ms       |

|---------------|----------|--------|--------|--------------|--------|-----------------|----------------------|------------|--------|----------------|--------------|

| 🛿 dk_perio    | 20000 ps |        |        |              |        |                 | 20000 ps             |            |        |                |              |

| dk            | 1        |        |        |              |        |                 |                      |            |        |                |              |

| le reset      | 0        |        |        |              |        |                 |                      |            |        |                |              |

| lie n         | 1        | NIT    |        | נת מנו מעת ב |        |                 | n nan an a           | NTUR AN AL |        | LID II TAIT AN | n nan un a n |

| la digon      | 1        |        |        |              |        |                 | 1                    |            |        |                |              |

| data_in[7     | 31       |        |        |              |        |                 |                      |            |        |                |              |

| ▶ 💐 max(11:0) | 016      |        |        |              |        |                 | 016                  |            |        |                |              |

| ▶ 🙀 r_dy(0:8) | [016,016 |        |        |              |        | [016,016,016,   | 016,000,000,000,00   | 0,000]     |        |                |              |

| 🕨 🙀 r_da(0:8) | [054,0a9 |        |        |              |        | [054,0a9,0fe, . | 1\$3,000,000,000,000 | 000)       |        |                |              |

| ▶ 💐 sum(0:8)  | [055,055 |        |        |              |        | [055,055,000,0  | 000,000,000,000,000  | 0,000]     |        |                |              |

|               |          |        |        |              |        |                 |                      |            |        |                |              |

|               |          |        |        |              |        |                 |                      |            |        |                |              |

Fig.19: shown the results of simulating of normal ECG signal.

Table III summarizes the FPGA resources used in the proposed systems.

Table III: Device Utilization Summary.

| Device Utilization Summary                     |       |           |             |         |  |  |  |

|------------------------------------------------|-------|-----------|-------------|---------|--|--|--|

| Logic Utilization                              | Used  | Available | Utilization | Note(s) |  |  |  |

| Total Number Slice Registers                   | 5,078 | 11,776    | 43%         |         |  |  |  |

| Number used as Flip Flops                      | 5,075 |           |             |         |  |  |  |

| Number used as Latches                         | 3     |           |             |         |  |  |  |

| Number of 4 input LUTs                         | 3,902 | 11,776    | 33%         |         |  |  |  |

| Number of occupied Slices                      | 4,429 | 5,888     | 75%         |         |  |  |  |

| Number of Slices containing only related logic | 4,429 | 4,429     | 100%        |         |  |  |  |

| Number of Slices containing unrelated logic    | 0     | 4,429     | 0%          |         |  |  |  |

| Total Number of 4 input LUTs                   | 4,287 | 11,776    | 36%         |         |  |  |  |

| Number used as logic                           | 3,902 |           |             |         |  |  |  |

| Number used as a route-thru                    | 385   |           |             |         |  |  |  |

| Number of bonded IOBs                          | 48    | 372       | 12%         |         |  |  |  |

| IOB Latches                                    | 3     |           |             |         |  |  |  |

| Number of BUFGMUXs                             | 1     | 24        | 4%          |         |  |  |  |

| Average Fanout of Non-Clock Nets               | 3.08  |           |             |         |  |  |  |

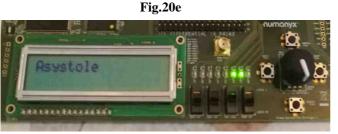

The Fig.19 can show the result of six types of heart abnormality is detected by using this proposed system.

Fig.20a

Fig.20c

## International Journal of Emerging Science and Engineering (IJESE) ISSN: 2319–6378, Volume-4 Issue-12, July 2017

Fig.20d

Fig.20f

Fig.20: Display result of six types of heart abnormality on LCD &LED.

## VII. CONCLUSION

A diagnosis system has been designed and implemented to acquire the ECG signal. Preprocessing of ECG is performed in the designed analog circuit which consists of instrument amplifier and filters for amplifying ECG and removing different types of noise from it. Arduino has been used as a mediator which converts the analog signal into a digital form and then sent data via XBee module (S2) as transmitter connect with Arduino via XBee shield to another XBee module (S2) as receiver connect with Spartan 3AN XC3S700 FPGA Starter Kit Board via UART. An algorithm for R Peak detection using Xilinx ISE software package has been proposed. Extraction of the R Peak obtained and used to compare with the normal waves.

#### REFERENCES

- 1. R. S. Khandpur, "Handbook of Biomedical Instrumentation", Tata McGraw-Hill publishing Company Limited, New Delhi 2005.

- 2. A. Stouffer, "Practical ECG Interpretation Clues to Heart Disease in Young Adults", ISBN: 978-1-405-17928-7, 2009.

- M. S. Nambakhsh et. al.," FPGA-Core Defibrillator using Wavelet-Fuzzy ECG Arrhythmia Classification", 2008 30<sup>th</sup> Annual International IEEE EMBS Conference Vancouver, BritishColumbia, Canada.

- C. Ken, and L. Xiaoying," A Zigbee Based Mesh Network for ECG Monitoring System", 4<sup>th</sup> international conference on Bioinformatics and Biomedical Engineering (iCBBE), 2010, Chengdu, China.

- H.K.Chatterjee et. al., "An FPGA implementation of real-time QRS detection", 2011 2<sup>nd</sup> International Conference on Computer & Communication Technology (ICCCT), Allahabad, India.

- C. G. Figueiredo, and T. Michael, "A vlsi architecture for arrhythmia detection and its implementation on fpga", 2013 Fourth International Conference on Computing, Communications and Networking Technologies (ICCCNT), Tiruchengode, India.

- EL M. El Hassan, and M. Karim, "An FPGA-Based Implementation of a Pre-Processing Stage for ECG Signal Analysis Using DWT", 2014 Second World Conference on Complex Systems (WCCS), Agadir, Morocco.

- H.K. Chatterjee et. al., "Real time Electrocardiogram wave peak detection algorithm and its implementation on FPGA", 2014 International Conference on Control, Instrumentation, Energy & Communication(CIEC), Calcutta, India 2014.

- Tongqing Li et. al.," The Real-Time R-wave Detection Based on FPGA", 2014 7th International Conference on BioMedical Engineering and Informatics (BMEI 2014), Dalian, China.

- Y. Liang et. al., "Field Programmable Gate Array Implementation Method of Electrocardiogram Signal Processing and Analysis", 2015 8th International Conference on BioMedical Engineering and Informatics (BMEI 2015), Shenyang, China.

- S. CHABCHOUB et. al.," Biomedical monitoring system using LabVIEW FPGA", 2015 World Congress on Information Technology and Computer Applications Congress (WCITCA), Hammamet, Tunisia.

- Mr. P.C.Bhaskar, and Mr.A.M. Kasture," Minimization of Base-Line Drift Interference from ECG Signal Using FPGA Based Adaptive Filter", 2015 International Conference on Computing Communication Control and Automation, Pune, India.

- Bhavtosh et. al.," High performance QRS Complex Detector for Wearable ECG systems using Multi Scaled Product with Booth Multiplier and Soft Threshold algorithm", 2015 International Conference on Signal Processing and Communication (ICSC), Noida, India.

- Dheyaa Alhelal et. al., "FPGA-Based Denoising and Beat Detection of the ECG Signal", 2015 IEEE Long Island Systems, Applications and Technology Conference (LISAT), Farmingdale, NY, USA.

- N. A. Abdul-Kadir et. al., "DSP ASIC Module Design for Natural Frequency of ECG Signal", 2015 IEEE International Circuits and Systems Symposium(ICSyS), Langkawi, Malaysia.

- N. Abdullah, and B. H. Abd, "A Simple FPGA System for ECG R-R Interval Detection", 2016 IEEE 11th Conference on Industrial Electronics and Applications (ICIEA), Hefei, China.

- R. Joaquinito, and H. Sarmento, "A Wireless Biosignal Measurement System using a SoC FPGA and Bluetooth Low Energy", 2016 International Conference on Consumer Electronics-Berlin.

- R. M. Y. Malkhasian," PC-Based Multi-Channel ECG System", M.Sc. thesis, University of Al-Nahrain, Iraq, 2005.

- L. Thulasimani and M. Dhivya, "Removal of Power-Line Interference from Biomedical Signal using using Notch Filter", Australian Journal of Basic and Applied Sciences, Pages: 161-165, 9(15) Special 2015.

- 20. A. Stouffer, "Practical ECG Interpretation Clues to Heart Disease in Young Adults", O'Reily Media, 2009.

- 21. T. L. Floyd, "Electronic Device", Pearson Education, 2008.

- T. Luong et. al., "Removal of power line interference from Electrocardiograph (ECG) using proposed adaptive filter," Global Journal of Computer Science and Technology, ISSN 0975-4172 (online), ISSN 0975-4350 (print), Vol.15-C,2015.

- 23. D. A. Bell, "Operational amplifiers and linear ICs", 2nd Edition, Oxford University Press, 1997.

- 24. B. Evans, "Beginning Arduino Programming", Apress, 2011.

- S. F. Barrett, "Arduino Microcontroller Processing for Everyone", Morgan & Claypool, 2010.

- 26. R. Faludi, "Building Wireless Sensor Networks", O'Reilly Media, 2011.

- 27. P. P. Chu, "FPGA Prototyping by VHDL Examples", Wiley-Interscience, 2008.

- R. X. Stroobandt, S. S. Barold and A. F. Sinnaeve, "ECG from Basics to Essentials Step by Step", John Wiley & Sons, 2016.